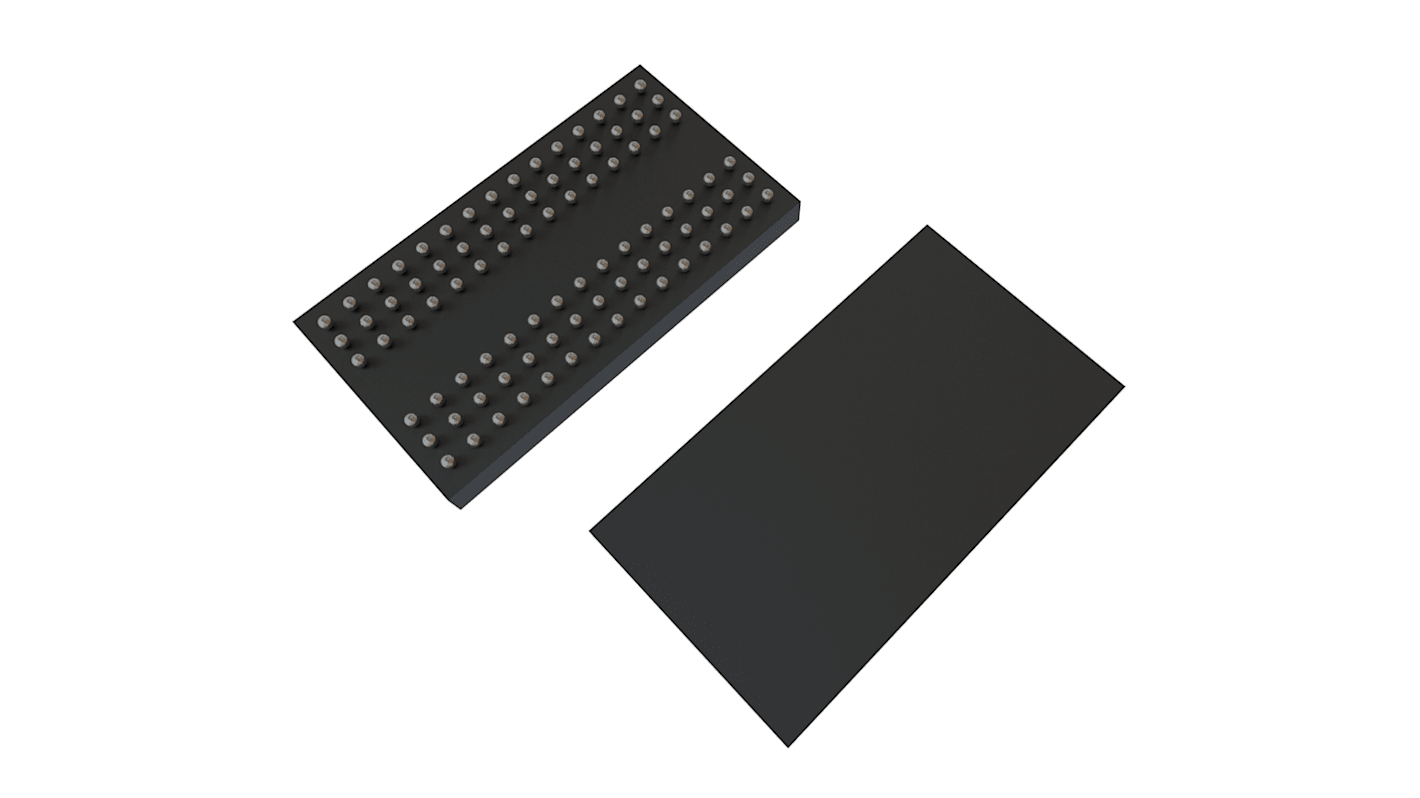

W9712G6KB25I, SDRAM, 128Mbit, Overflademontering, 200MHz, 1,7 V til 1,9 V, -40 °C til +95 °C, 84 ben, TFBGA DDR2

- RS-varenummer:

- 188-2730

- Producentens varenummer:

- W9712G6KB25I

- Brand:

- Winbond

Varen er desværre i restordre, forventet afsendelsesdato 02-12-2024

Dag til dag levering ikke mulig

Tilføjet

Pris pr. stk. (Leveres i pakke af 5)

Kr. 15,664

(ekskl. moms)

Kr. 19,58

(inkl. moms)

| Enheder | Pr stk. | Pr pakke* |

| 5 - 5 | Kr. 15,664 | Kr. 78,32 |

| 10 - 15 | Kr. 14,242 | Kr. 71,21 |

| 20 - 45 | Kr. 13,988 | Kr. 69,94 |

| 50 - 95 | Kr. 13,808 | Kr. 69,04 |

| 100 + | Kr. 12,402 | Kr. 62,01 |

- RS-varenummer:

- 188-2730

- Producentens varenummer:

- W9712G6KB25I

- Brand:

- Winbond

Tekniske referencer

Lovgivning og oprindelsesland

Generel produktinformation

W9712G6KB er en 128M-bit DDR2 SDRAM og hastighed, der involverer -25, 25I og -3.

Dobbelt datahastighedsarkitektur: To dataoverførsler pr. clock-periode

CAS-latens: 3, 4, 5 og 6

Burstlængde: 4 og 8

2-vejs, differential datablink (DQS og /DQS) sendes/modtages med data

Kantjusteret med læse-data og centerjusteret med skrive-data

DLL justerer DQ- og DQS-overgange med clock

Differentiale clock-indgange (CLK og /CLK)

Datamasker (DM) til skrive-data

Kommandoer, der indtastes på hver positiv CLK-kant, data- og datamaske, refererer til begge kanter af /DQS

Opslået/CAS-programmerbar additiv latenstid understøttes for at gøre kommando- og databussens effektivitet

Læse latens = Additiv latens plus CAS Latency (RL = al + CL)

Off-Chip-Driver impedansjustering (OCD) og On-Die-Termination (ODT) for bedre signalkvalitet

Automatisk forladningsdrift til læse- og skrive-burst

Automatisk opdatering og selvopdatering

Forladet nedlukning og aktiv nedlukning

Skriv Datamaske

Skriveventetid = Læseventetid - 1 (WL=RL-1)

Grænseflade: SSTL_18

CAS-latens: 3, 4, 5 og 6

Burstlængde: 4 og 8

2-vejs, differential datablink (DQS og /DQS) sendes/modtages med data

Kantjusteret med læse-data og centerjusteret med skrive-data

DLL justerer DQ- og DQS-overgange med clock

Differentiale clock-indgange (CLK og /CLK)

Datamasker (DM) til skrive-data

Kommandoer, der indtastes på hver positiv CLK-kant, data- og datamaske, refererer til begge kanter af /DQS

Opslået/CAS-programmerbar additiv latenstid understøttes for at gøre kommando- og databussens effektivitet

Læse latens = Additiv latens plus CAS Latency (RL = al + CL)

Off-Chip-Driver impedansjustering (OCD) og On-Die-Termination (ODT) for bedre signalkvalitet

Automatisk forladningsdrift til læse- og skrive-burst

Automatisk opdatering og selvopdatering

Forladet nedlukning og aktiv nedlukning

Skriv Datamaske

Skriveventetid = Læseventetid - 1 (WL=RL-1)

Grænseflade: SSTL_18

Egenskaber

Attribute | Value |

|---|---|

| Memory-størrelse | 128Mbit |

| Organisation | 8 M x 16 bit |

| SDRAM klasse | DDR2 |

| Datahastighed | 200MHz |

| Databusbredde | 16bit |

| Adressebusbredde | 15bit |

| Antal Bits per ord | 8bit |

| Random access-tid maks. | 0.4ns |

| Antal ord | 16M |

| Monteringstype | Overflademontering |

| Kapslingstype | TFBGA |

| Benantal | 84 |

| Dimensioner | 12.6 x 8.1 x 0.8mm |

| Højde | 0.8mm |

| Længde | 12.6mm |

| Bredde | 8.1mm |

| Driftsforsyningsspænding maks. | 1,9 V |

| Driftstemperatur min. | -40 °C |

| Driftsforsyningsspænding min. | 1,7 V |

| Driftstemperatur maks. | +95 °C |