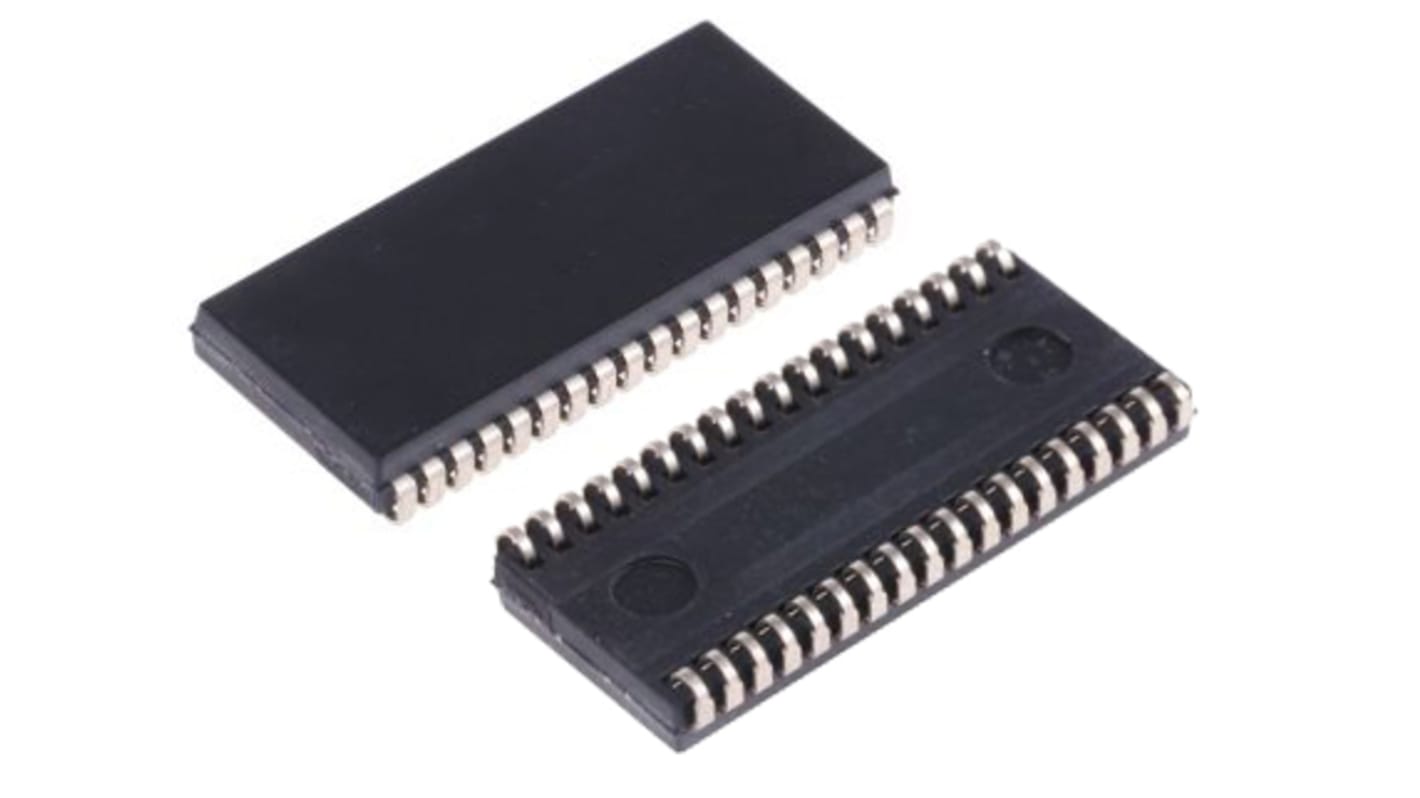

Infineon SRAM -hukommelseschip, 4Mbit, SOJ 36

- RS-varenummer:

- 193-8466

- Producentens varenummer:

- CY7C1049G30-10VXI

- Brand:

- Infineon

Ikke tilgængelig

RS lagerfører ikke længere dette produkt

- RS-varenummer:

- 193-8466

- Producentens varenummer:

- CY7C1049G30-10VXI

- Brand:

- Infineon

Egenskaber

Tekniske referencer

Lovgivning og oprindelsesland

Generel produktinformation

Find lignende produkter ved at vælge én eller flere attributter.

Vælg alle | Attribut | Værdi |

|---|---|---|

| Brand | Infineon | |

| Memory-størrelse | 4Mbit | |

| Organisation | 512 k x 8 bit | |

| Antal ord | 512k | |

| Antal Bits per ord | 8bit | |

| Random access-tid maks. | 10ns | |

| Adressebusbredde | 8bit | |

| Clock-frekvens | 100MHz | |

| Timing-type | Asynkron | |

| Monteringstype | Hulmontering | |

| Kapslingstype | SOJ | |

| Benantal | 36 | |

| Dimensioner | 0.92 x 0.395 x 0.103tommer | |

| Højde | 2.62mm | |

| Driftsforsyningsspænding maks. | 3,6 V | |

| Driftsforsyningsspænding min. | 2,2 V | |

| Længde | 23.37mm | |

| Driftstemperatur maks. | +85 °C | |

| Bredde | 10.03mm | |

| Driftstemperatur min. | -40 °C | |

| Vælg alle | ||

|---|---|---|

Brand Infineon | ||

Memory-størrelse 4Mbit | ||

Organisation 512 k x 8 bit | ||

Antal ord 512k | ||

Antal Bits per ord 8bit | ||

Random access-tid maks. 10ns | ||

Adressebusbredde 8bit | ||

Clock-frekvens 100MHz | ||

Timing-type Asynkron | ||

Monteringstype Hulmontering | ||

Kapslingstype SOJ | ||

Benantal 36 | ||

Dimensioner 0.92 x 0.395 x 0.103tommer | ||

Højde 2.62mm | ||

Driftsforsyningsspænding maks. 3,6 V | ||

Driftsforsyningsspænding min. 2,2 V | ||

Længde 23.37mm | ||

Driftstemperatur maks. +85 °C | ||

Bredde 10.03mm | ||

Driftstemperatur min. -40 °C | ||

CY7C1049G og CY7C1049GE er højtydende CMOS hurtige statiske RAM-enheder med integreret ECC. Begge enheder tilbydes i enkelt- og dobbeltchip-aktiveringsmuligheder og i konfigurationer med flere ben. CY7C1049GE enheden indeholder en ERR-stift, der signalerer en fejl-detektion og korrektion under en læsningscyklus. Dataskrivning udføres ved at gøre input for Chip Enable (CE) og Write Enable (WE) LAVE, mens data for i/O0through i/O7 og adresse på A0 via A18-ben gives. Dataaflæsninger udføres ved at angive input for Chip Enable (CE) og Output Enable (OE) LAVT og angive den ønskede adresse på adresselinjerne. Der er adgang til læste data på i/O-linjerne (i/O0 til i/O7).

Høj hastighed

TAA = 10 ns

Integreret ECC for single-bit fejlkorrektion [1, 2]

Lav aktiv- og standbystrøm

Aktiv strøm: ICC = 38 mA typisk

Standbystrøm: ISB2 = 6 mA typisk

Driftsspændingsområde: 1,65 V til 2,2 V, 2,2 V til 3,6 V og 4,5 V til 5,5 V.

1,0 V dataopbevaring

TTL-kompatible indgange og udgange

Fejlindikationens (ERR) pin indikerer 1-bit fejlregistrering og -korrektion

Blyfri 36-benede SOJ og 44-benede TSOP II huse

TAA = 10 ns

Integreret ECC for single-bit fejlkorrektion [1, 2]

Lav aktiv- og standbystrøm

Aktiv strøm: ICC = 38 mA typisk

Standbystrøm: ISB2 = 6 mA typisk

Driftsspændingsområde: 1,65 V til 2,2 V, 2,2 V til 3,6 V og 4,5 V til 5,5 V.

1,0 V dataopbevaring

TTL-kompatible indgange og udgange

Fejlindikationens (ERR) pin indikerer 1-bit fejlregistrering og -korrektion

Blyfri 36-benede SOJ og 44-benede TSOP II huse

Relaterede links

- Infineon SRAM -hukommelseschip SOJ 36

- Infineon SRAM -hukommelseschip SOJ 32

- Cypress Semiconductor SRAM -hukommelseschip, 4Mbit

- Infineon SRAM 36-benet støbt SOJ/44-Pin TSOP II 44 Ben

- Infineon SRAM -hukommelseschip SOJ 44

- Infineon SRAM -hukommelseschip SOJ 85

- Infineon SRAM SOJ 36 Ben

- Infineon SRAM -hukommelseschip TSOP II 44